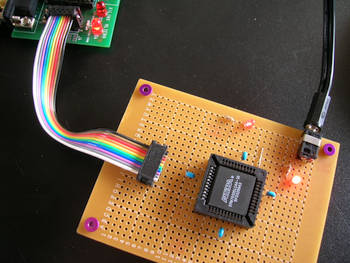

EPM7032Sデザインルールを調べたのでまとめる。

・VCCとGNDは全て接続する

・使用していないI/OピンをPin-Out Fileでしらべると”RESERVED”になっている→何処にも接続してはならない

・入力専用ピン→使わないなら、GNDに落とす

・Jtag関連(TDO)はoutput端子→何処にも接続しない

・Jtag関連(TMS,TDI,TCK)はinput端子

・TMS,TDIはTCKの立ち上がりで読み込まれる→TCKはGND

・JTAGのステートマシーンが動作しだしても、TMS=1ならIdle状態に戻る→TMSはVCC

・グローバルクロック→そのままクロックを繋ぐ

・グローバルリセット(LOWレベルでFFをリセット)→プルアップ処理

・出力イネーブル専用ピン(Lowレベルで動作)→GND

・Jtag書き込み中の端子は50kΩでプルアップされる。

質問

・上ではJtag関連端子を処理しようとしていますが、Jtagピンを開放のまま(or TCKだけGND)にすることにより、使用上問題は発生するのでしょうか?

参照

Pin-Out File

JTAG のテクニカルガイド:http://www.xjtag.com/jp/support-jtag/jtag-technical-guide.php

アルテラ・デバイスの使用上の注意:http://www.altera.co.jp/literature/ds/dsoprq_j.pdf