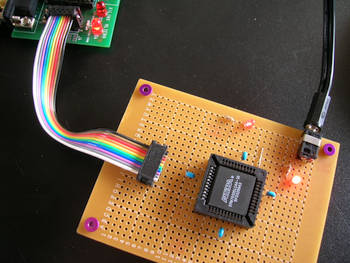

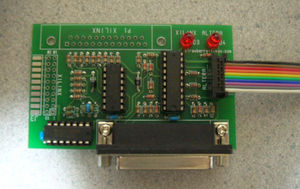

これがこう↓なるはず。

// moter_drive01

module moter_drive01(ck,pwm,cw_ccw,Lp,Ln,Rp,Rn);

input ck,pwm,cw_ccw;

output Lp,Ln,Rp,Rn;reg [3:0] shift_pwm;

//4clock shift

always@(posedge ck) begin

shift_pwm[3] <= shift_pwm[2];

shift_pwm[2] <= shift_pwm[1];

shift_pwm[1] <= shift_pwm[0];

shift_pwm[0] <= pwm;

endfunction [3:0] outport;

input [2:0] outport_in;

case(outport_in) //pn pn

3’b 000: outport = 4’b11_11; //XO XO

3’b 001: outport = 4’b10_11; //XX XO

3’b 011: outport = 4’b00_11; //OX XO

3’b 010: outport = 4’b10_11; //XX XO3’b 100: outport = 4’b11_11;

3’b 101: outport = 4’b11_10;

3’b 111: outport = 4’b11_00;

3’b 110: outport = 4’b11_10;default: outport = 4’bxx_xx;

endcase

endfunctionassign {Lp,Ln,Rp,Rn} = outport({cw_ccw,shift_pwm[3],pwm});

endmodule

//////////////////////

DigiKey検索プラグインを更新