メカ&ハード7割完成

こりゃまずい

平日に埃の舞う作業ができなかったり、体調不良で病院に行ったら採血中に気を失ったり、なんだかんだで作業が遅れている。(申し訳ありません。各所への返信も遅れています)

メイン基板の実装を始めるが、ミスを繰り返す。以前の分に追加して、

・PLCCソケットの選定ミス(熱に弱い、はんだ付けし難い)

・PLCCソケットの向きを90度間違えて実装

・CPUボードのピン位置間違い(1mm弱全体的にずれている。CPUボードを載せるために、CPUボード&LDOを削ることに)

・ピンソケット用の穴が小さい(基板に挿入しにくい)

CPLDの動作は確認できた、途中pwmの出力が正しく出ず、マイコン側のプログラム上で2455*15をintに入れようとしていたという原因を見つけるのに時間が掛かった。

大会までに間に合うのか、微妙な線を行っている。

こつこつ

Olimexから発送メールが来る。

この基板について、現時点で分かっているミス。

・ICのフットパターン上に1608チップを誤挿入(上図、パターン間短絡の恐れ)

・PSD信号線をプルダウンしている(オープンコレクタならプルアップが必要)

スタンレーのku381-80を入手しようとするも、見つからず。べステクでも在庫無し。しばらくは、昨年の物を使いまわすことになりそうだ。

搬送ケース

マイコンカーの搬送に使えそうな箱を探す。

大きな工具箱に詰めてもいいが、飛行機機内に工具は持ち込めないため、大きすぎない物を探し出す。

・アステージ株式会社 NTボックス #30 外寸:715×337×177

・アステージ株式会社 NCボックス #30 外寸:715×337×177

・三菱樹脂 ヒシコンテナ TP-361B 外寸:670×335×103 別売り蓋アリ

・三菱樹脂 ヒシコンテナ TP-361.5B 外寸:670×335×149 別売り蓋アリ

・岐阜プラスチック工業 TPコンテナ TP-361B 別売り蓋アリ

結局ジャストサイズは見つからず、ダンボール箱業者への製作依頼を考える。

写真はamazonの箱を再利用して作った私試作品。こんな感じの箱を欲しい人が近所(受け渡しが簡単にできる)で20人位あれば、業者に依頼したい。

基板発注

Olimexに見積り依頼を出す。結線のチェックは簡易にしただけ。駄目なら修正して再発注する。

次、基板が届くまでに、素子を揃える作業に移る。

/////////////////////////////

Tsubameさん経由で、GTmicom_Uさんの写真見せていただく。

昨年に増して、完成度高く見事な作り。速いわけだ。

ご一緒できる機会に、センサの処理について聞かせてください。

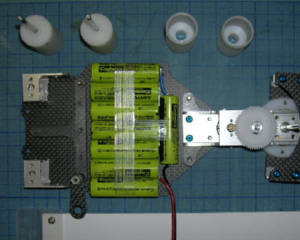

ヒシチューブでパック化

オヤイデ電気で購入したヒシチューブ83mmで組電池をパック化する。

今回は105mmにカットして使用した。もう数ミリ長くても良さそうである。

DAKARAのパックと比べて

・透明

・厚い

・重い(約7g@105mm)

こつこつ

・ハーフライン読み取り後速度制御

・車線変更立ち上がりESC

・カーボン板の穴位置修正

・バッテリの組電池化

・ヒシチューブ等オヤイデ電気に発注

デザインルール

EPM7032Sデザインルールを調べたのでまとめる。

・VCCとGNDは全て接続する

・使用していないI/OピンをPin-Out Fileでしらべると”RESERVED”になっている→何処にも接続してはならない

・入力専用ピン→使わないなら、GNDに落とす

・Jtag関連(TDO)はoutput端子→何処にも接続しない

・Jtag関連(TMS,TDI,TCK)はinput端子

・TMS,TDIはTCKの立ち上がりで読み込まれる→TCKはGND

・JTAGのステートマシーンが動作しだしても、TMS=1ならIdle状態に戻る→TMSはVCC

・グローバルクロック→そのままクロックを繋ぐ

・グローバルリセット(LOWレベルでFFをリセット)→プルアップ処理

・出力イネーブル専用ピン(Lowレベルで動作)→GND

・Jtag書き込み中の端子は50kΩでプルアップされる。

質問

・上ではJtag関連端子を処理しようとしていますが、Jtagピンを開放のまま(or TCKだけGND)にすることにより、使用上問題は発生するのでしょうか?

参照

Pin-Out File

JTAG のテクニカルガイド:http://www.xjtag.com/jp/support-jtag/jtag-technical-guide.php

アルテラ・デバイスの使用上の注意:http://www.altera.co.jp/literature/ds/dsoprq_j.pdf